专注于胶粘剂的研发制造

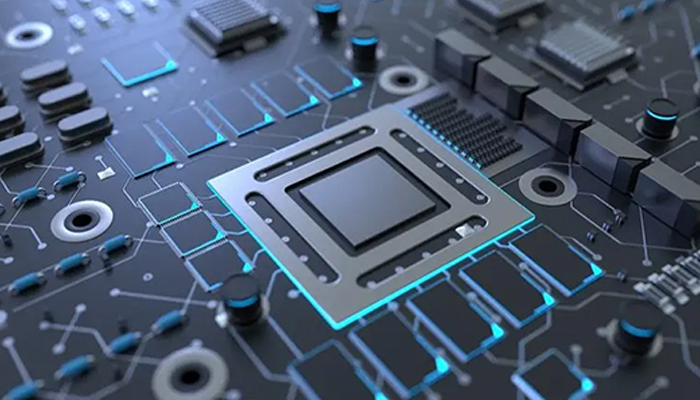

在半导体封装领域,芯片底部填充胶(Underfill)作为关键材料,通过填充芯片与基板间的微米级间隙,显著提升了电子产品的可靠性。接下来,研泰化学胶粘剂应用工程师将浅析其性能特点与工艺控制要点。

一、核心性能特点

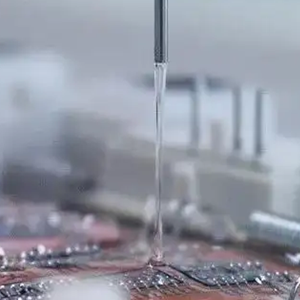

1. 高流动性与精准填充能力

底部填充胶采用低黏度环氧树脂体系,黏度普遍低于0.5 Pa·s,可借助毛细作用在10-50秒内渗透至BGA芯片底部10μm级间隙。

2. 热-机械应力缓冲机制

针对硅芯片(CTE 2.5×10⁻⁶/K)与PCB基板(CTE 18-24×10⁻⁶/K)的热膨胀系数差异,优质填充胶通过以下设计实现应力平衡:

• 低CTE配方:球型二氧化硅填料占比达70-85%,将CTE控制在12-18×10⁻⁶/K

• 梯度玻璃化转变温度(Tg):采用双酚A/F环氧树脂共混体系,形成80-150℃分段固化特性,适应不同热循环场景

• 高弹性模量:固化后模量达8-12 GPa,有效分散焊点应力,使BGA组件抗跌落性能提升300%

3. 快速固化与工艺兼容性

主流产品支持80℃/10min-150℃/2min的梯度固化方案,汉高HT系列更开发出UV-热双固化体系,实现30秒初固+5分钟完全固化。与SAC305等无铅焊料兼容性测试显示,在260℃回流焊3次后,剪切强度衰减率低于8%。

4. 可靠性验证体系

通过JESD22-B111标准测试:

• 热循环:-40℃~125℃/1000次循环后失效率<0.5%

• 机械冲击:1500G/0.5ms冲击后开路率<0.1%

• 湿度敏感度:85℃/85%RH/168h后吸水率<0.15%

二、应用工艺关键控制点

1. 前处理工艺优化

• 真空烘烤:采用三段式烘烤(60℃/1h→85℃/2h→125℃/4h),将PCBA含水率降至0.05%以下,避免固化气泡

• 等离子清洗:O₂/CF₄混合气体等离子处理(功率300W,时间3min),使基板表面能提升至65mN/m以上

• 助焊剂残留控制:采用免清洗助焊剂+在线式离子污染测试仪(IPC-TM-650 2.3.28),确保离子残留量<1.5μg NaCl/cm²

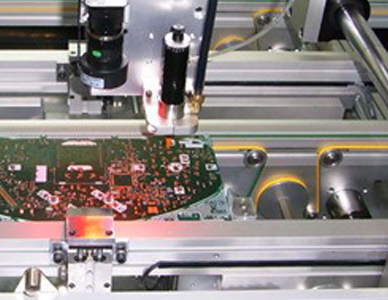

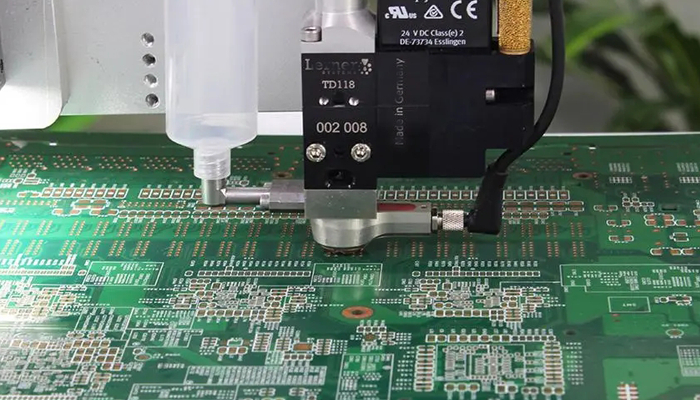

2. 精密点胶技术

设备选型:采用压电喷射阀(精度±25μm)或螺旋泵(流量稳定性±1%)

路径规划:

• BGA封装:采用"L"型路径,点胶速度100-300mm/s

• Flip-Chip封装:采用螺旋填充路径,转速500-2000rpm

• 胶量控制:单点胶量公式:V=4π×(D+2δ)2×h×(1+ε)

(D:焊球直径,δ:间隙,h:芯片厚度,ε:冗余系数1.05-1.1)

3. 固化工艺窗口管理

• 红外热成像监控:在固化炉内设置5个温度监测点,确保温差<±3℃

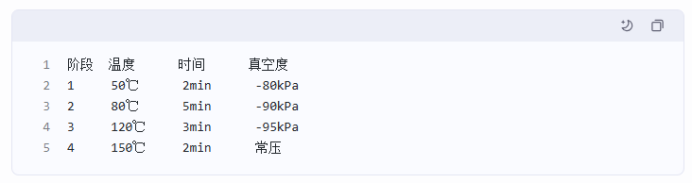

• 阶梯固化曲线:

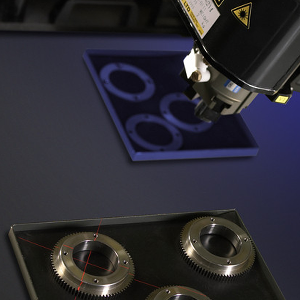

• 在线X-Ray检测:采用160kV微焦点X射线系统,检测空洞率标准:

• 单个空洞直径<0.2mm

• 总面积空洞率<5%

三、行业发展趋势

1.材料创新:

研发室温自修复聚氨酯体系,在-40℃~125℃热冲击下实现裂纹自愈合,寿命延长至10年以上。

2.工艺升级:

轴心自控推出的AI视觉点胶系统,通过深度学习算法实现:

• 元件识别准确率99.97%

• 路径规划时间缩短80%

• 胶量控制CV值<3%

3.环保要求:

欧盟RoHS 3.0标准实施后,行业加速淘汰含卤素阻燃剂,纳米氮化硼替代方案使阻燃等级达到UL94 V-0,同时保持CTE稳定性。

芯片底部填充胶技术已进入纳米级精度控制时代,其性能优化与工艺创新直接关系到5G基站、自动驾驶域控制器等高端电子产品的可靠性。企业需建立从材料研发到工艺验证的全链条质量管控体系,方能在半导体封装微缩化趋势中占据竞争优势。如需了解更多关于芯片底部填充胶应用方面的问题,欢迎留言或来电咨询研泰化学技术人员。作为专业的电子胶粘剂生产厂家,研泰近20载专注于研发生产各类电子胶粘剂,为了方便大家更好的使用和保存胶粘剂,同步也会在官网分享一些胶粘剂的相关知识给大家,欢迎大家随时关注—研泰官网。